| 제목 | 답변완료 회로이론 테브난 | ||

|---|---|---|---|

| 질문유형 | 강좌내용 | 교수님 | 양진목 |

| 과목 | 회로이론 | 강좌명 | |

| 작성자 | 강*규 (g*******0) | 등록일 | 2022-04-16 18:54 |

| 첨부파일 | |||

|

질문내용과 문제를 첨부하였습니다 .

해당풀이과정이 맞는지 확인해주시면 감사하겠습니다! 답변 완료된 질문과 답변은 수정 및 삭제가 불가합니다. |

|||

- 댓글

- 0

강*규

안녕하세요. 양진목입니다.

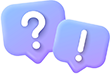

1. 우선 KCL 식에서 12V 전압원에도 전류가 흐르기 때문에 이 전류를 고려하셔야 합니다.

그래서 supernode를 잡을 때 12V전압원도 포함시켜야 합니다.

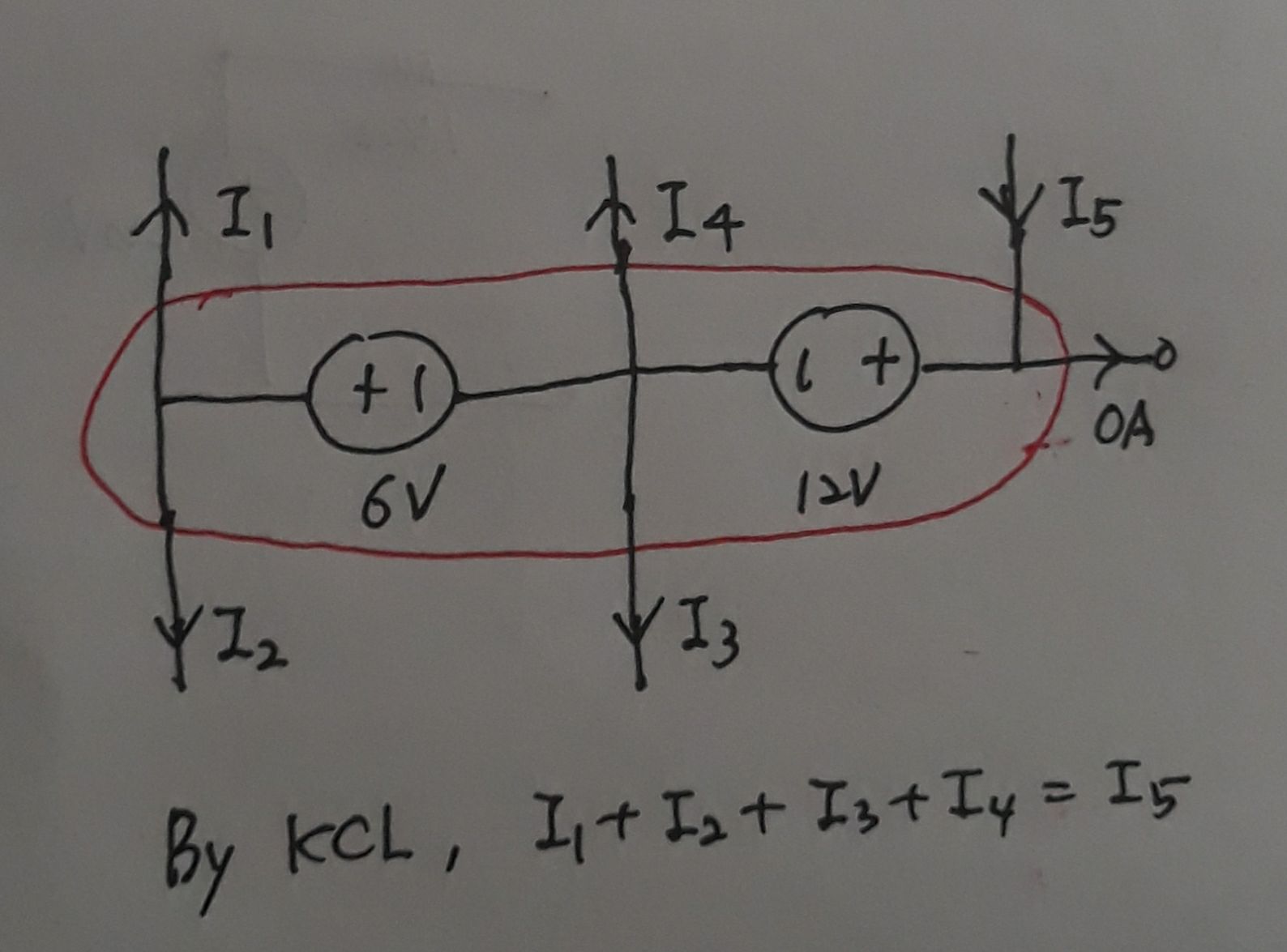

2. (결론은 맞지만) Rth구할 때 회로 윗부분의 1k, 2k옴이 개방된 것이 아니라 이 둘이 연결되어 있어야 합니다.(전류원이 개방되므로)

그러면 1k, 2k옴이 직렬연결이어서 합성저항은 3k옴이 되는데 3k옴 양단전압이 0V이므로 이는 제거할 수 있습니다. 따라서 결론적으로

아래 부분의 1k, 2k옴만 병렬연결된 구조가 남습니다.

답변이 되었는지 모르겠습니다.

그럼 안녕히계세요.

- 2022-04-18

- 2024-12-12 수정